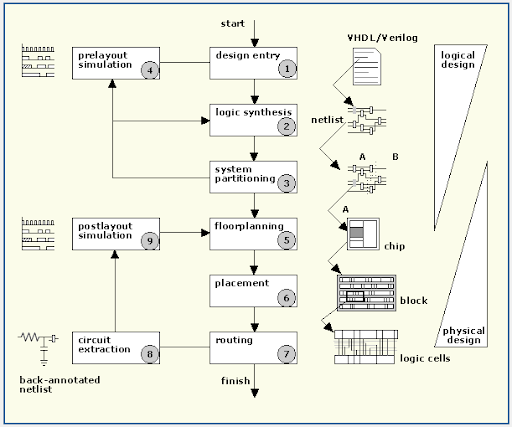

En la figura 12 se muestra una secuencia lógica con los pasos para el diseño de un ASIC. Los pasos del 1-4 son parte del diseño lógico, los pasos del 5 - 9 son parte del diseño físico [4].

Figura12: Pasos involucrados en el diseño de un ASIC.

- Entrada del diseño: Un diseño es cargado en un sistema de diseño de ASIC's puede utilizarse un lenguaje de descripción de hardware HDL.

- Sintesis lógica: Usa un HDL (VHDL o Verilog) y una herramienta de síntesis lógica que produce una lista de redes la cual consiste en una descripción de las celdas lógicas y sus interconexiones.

- Partición del sistema: Divide un sistema en piezas detalladas del ASIC.

- Simulación prelayaut: chequea si el sistema funciona correctamente.

- Planeamiento de piso: Acomoda los bloques de la lista de redes de conexión en un chip.

- Ubicación: Decide la localización de las celdas en un bloque.

- Ruteo: Establece las conexiones entre las celdas y los bloques.

- Extracción: Determina la resistencia y la capacitancia de las interconexiones.

- Simulación Post-layout: en este paso se revisa si el diseño es capaz defuncionar con las cargas agregadas a las interconexiones