A continuación se describen algunos de los circuitos o elementos que no son muy bien aceptados para ser incluidos en un ASIC.

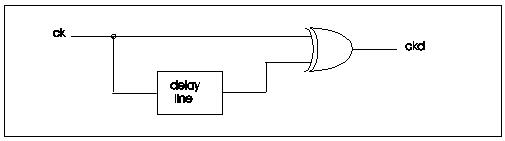

Multiplicadores de frecuencia:

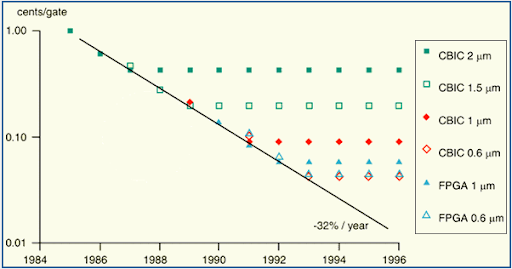

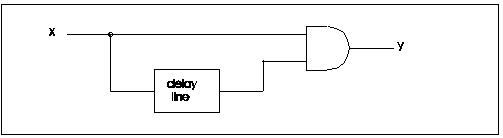

Una técnica ocacionalmente utilizada es un diseño lógico discreto para producir el doble de la frecuencia de reloj generando un pulso corto utilizando una linea de retardo y una compuerta OR exclusiva. Esta técnica no es muy deseada pero permitida en el diseño con ASIC´s cuando así se requiera. Solo se emplea en UARTS el cual requiere un diseño especial y procedimiento de pruebas. Las multiplicaciones de frecuencia suelen ser implementadas utilizando PLL´s externos. En la figura 15 puede verse un ejemplo de lo descrito anteriormente.

Figura 15: Multiplicador de frecuencia.

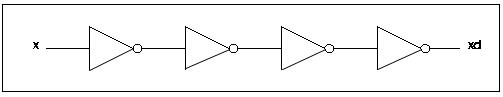

Lineas de retardo:

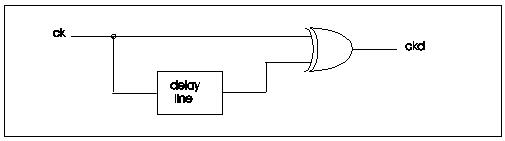

Las lineas de retardo son extermadamente sensibles a las variaciones de proceso tales como la temperatura. Consiste en multiples compuertas sucesivas que producen una latencia en la propagación de la señal. Esto no es necesario cuando se emplean técnicas de diséño sincrinizado. Cuando se utilizan arreglos de retardos las pruebas tienen una mayor dificultad. En la figura 16 puede verse una tipica linea de retardo.

Figura 16: Linea de retardo.

Monoestables:

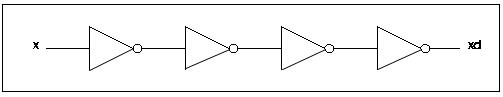

Los diseños de moestables al igual que las lineas de retardo y los multiplicadores de frecuencia están bastante limitados en el diseño con ASIC´s su implementación generalmente se hace fuera del IC.

Figura 17: Monoestable

Osciladores sobre el chip:

Al igual que los circuitos monoestables y las lineas de retardo, estos son pñrocesos dependientes de la frecuencia, muchos constructores de ASIC´s, suministran estos osciladores como parches de libreria. Es preferible utilizar osciladores de tipo cristal.

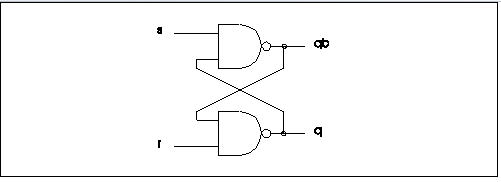

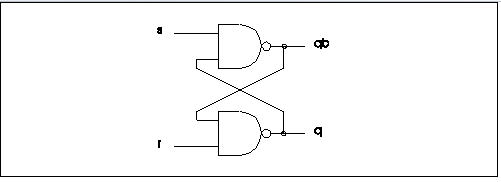

Flip-flop RS:

La seria desventaja del uso de este flip-flop´s asíncronicos es que su estado de salida no puede garantizarse cuando ambas entradas van a estado alto. los glitches o ruidos pueden producir estados indeseables en las salidas, por ello su uso en el núcleo no es favorable y tampoco es requerido porque se dispone de este mismo elemento pero en version síncrona. En la figura 18 se muestra un ff RS.

Figura 18: Flip-flop RS formado asincronico.

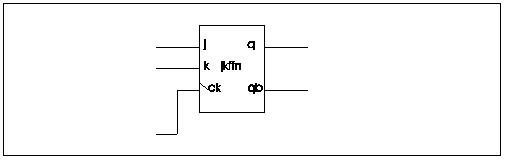

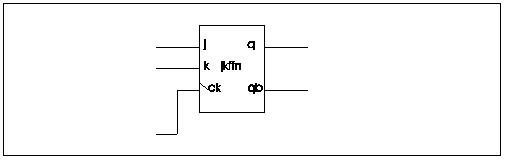

flip-flop JK:

No son deseables porque su uso involucra un mayor uso que el uso de un tipo D en el ASIC, adicionalmente sus entradas asincronicas pueden causar otros problemas de inestabilidad en el sistema. Figura 19, flip-flop JK.

Figura 19: FF JK

Flip-flop implícito:

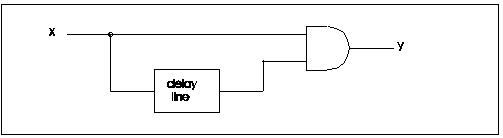

Un error de diseño podria ocurrir sin que el diseñador tenga cuidado de las consecuencias de la creación de un flip-flop implícito al conectar un lazo de realimentación en un circuito combinacional. El resultado es un flip-flop RS y deberia ser evitado.

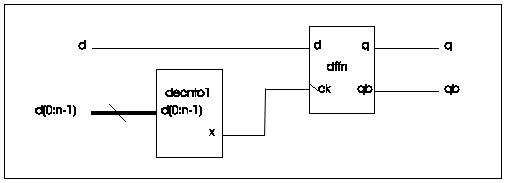

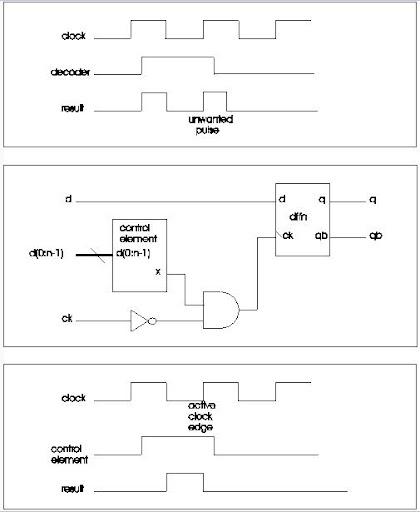

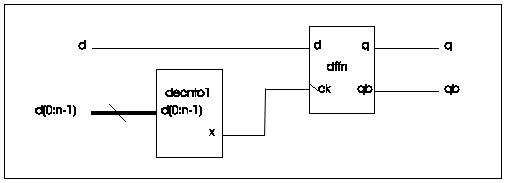

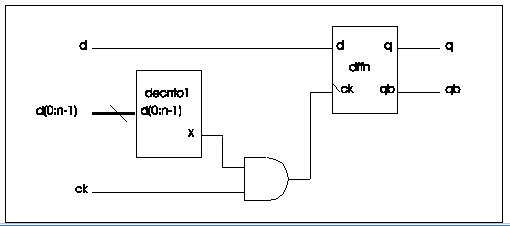

Mal uso de los elementos de control:

Decodificadores y comparadores son puestos a funcionar en situaciones peligrosas. Esto se debe a las diferencias de longitudes entre las rutas de datos y consecuentes variaciones en los retardos de las compuertas desde sus entradas o sus salidas. Conectando a un decodificador o un comparador directamente a uçla entrada de un reloj o un borrado asincrónico, quizás esto puede hacerse al lachear data condicionalmente en un flanco de reloj, esto es un error de diseño con serias consecuencias. En la figura 20 se muestra uno de estos casos.

Figura 20: Mal uso de elementos.

Salida de un latch alimentando la señal de reloj de otro:

Convencionalmente los diseñadores tienen que intentar eliminar situaciones peligrosas y glitches al lachear las salidas de comparadote y decodificadores utilizando un flip-flop tipo D. sin embargo, la salida del flip-flop cambia durante el muestreo y el tiempo de mantenimiento del latch de muestreo. La data en la salida de la fuente del flip-flop es inválida porque este comenzó el muestreo en el punto de cambio y la salida del flip-flop es inválida debido a la violación del seteo y el muestreo. Otro problema es cuando la misma data es lacheada en dos pulsos de reloj consecutivos. El decodificador o comparador cambia de nivel bajo a alto por la primera condición de la data muestreada, como no hay cambio en la salida del decodificador entonces este no responde a la segunda petición. Figura 21 muestra el caso.

Figura 21: Salida de un latch a señal de reloj de otro.

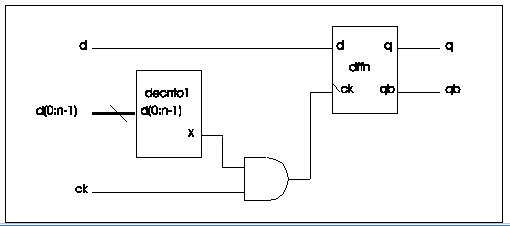

Gated clock:

Cuando es controlada una señal de reloj por la petición de un latch mediante una compuerta crea una mala situación porque aparece un corto punto al término de dos peticiones condicionales debido al retardo del reloj a la salida Q y el tiempo del flip-flop tipo D. En la figura 22 puede observarse una señal de reloj controlada por una compuerta y la condición de otro elemento.

Figura 22: Gated Clock.

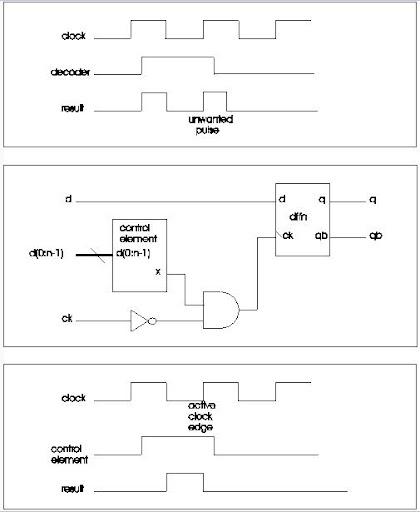

Flanco negativo del reloj:

Una forma de intentar evitar el problema es utilizando latch tipo D sensibles al flanco de bajada del reloj. Esto resuelve que el flip-flop tenga problemas de seteo y muestreo de la data pero no resuelve el problema de muestreo de dos condiciones.

Los tipo D sensibles al flanco de bajada del reloj tienen dos desventajas, ellos reducen a la mitad el periodo disponible del reloj y por lo tanto los circuito como los filtros digitales no pueden operar a la misma velocidad que un latch síncrono. También los flancos negativos producen un fenómeno llamado conformación de pulsos. Esto se debe a la baja movilidad de los transistores tipo P y pueden producir un retardo diferencial entre la respuesta a los flancos de subida y de bajada. en la figura 23 se observan los diagramas de tiempo y los ejemplos de elementos involucrados.

Figura 23: Problemas con flancos de bajada.

Borrado asíncrono usando pulsos de reset cortos:

Un intento para borrar asincrónicamente y condicionalmente en contra del estado del circuito, encuentra un problema similar al del clock Gated. De acuerdo con esto se producen desventajas en los borrados asíncronos de los Flip-flop´s RS.

Borrado asíncrono-pulsos de reset largos:

Para este caso la función de reset es derivada a un latch adicional, esto es un avance en la versión previa pero la desventaja es que el flip-flop es mantenido en estado de reset hasta que se cumple el próximo periodo del reloj dejándolo no disponible durante un periodo. A este fenómeno se le llama ciclo muerto.

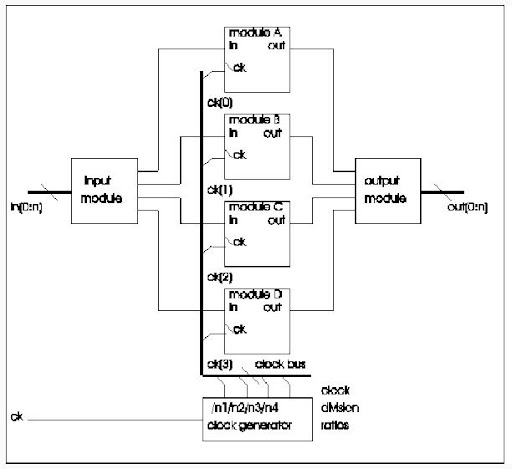

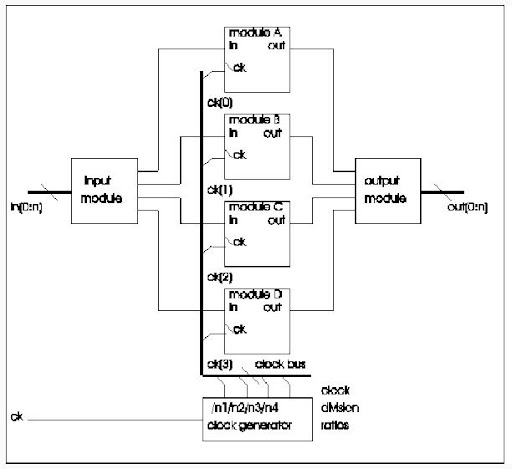

Generador de reloj central:

Muchos diseños lógicos están basados en un generador central de pulsos de reloj. Este tiene como generador primario un reloj externo y genera un número de señales secundarias de fracciones de la velocidad del reloj primario por procesos de división. Aunque el generador de reloj puedo haber sido diseñado utilizando principios de diseño sincronizado, el generador de reloj central tiene una seria desventaja, las señales de reloj secundarias pueden estar muy sesgadas respecto a la primaria lo cual implica que la señal primaria no pueda ser utilizada. La figura 24 muestra el caso.

Figura 24:Generador de reloj central.