Para el caso de los ASIC mas utilizados tenemos a los semiconfigurables. En estos las celdas lógicas ya han sido preconfiguradas y solo pueden alterarse las configuraciones de todas las máscaras de interconexión. Al utilizar este método, el trabajo del diseñador se hace mucho más fácil. Aun para esta clase de ASIC's existen dos subcategorias las cuales son:

- ASIC's basados en celdas estándar.

- ASIC's basados en arreglos de compuertas.

ASIC's basados en celdas estándar (Standard-Cell-Based ASICs).

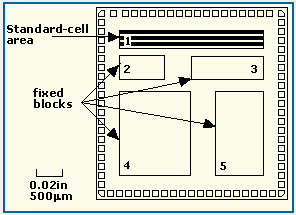

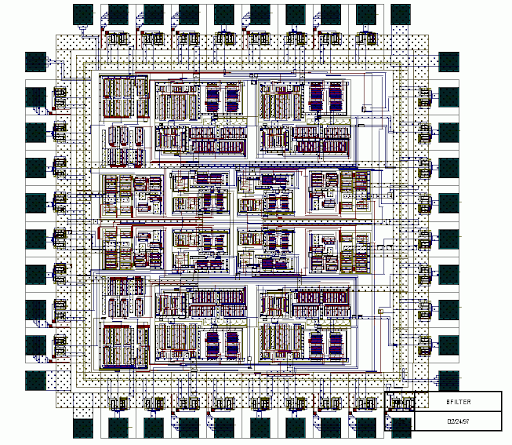

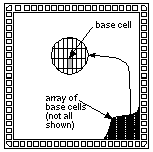

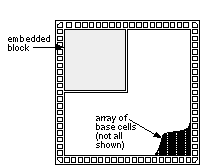

En Japón es un termino conocido coloquialmente como CBIC pronunciado como "sea-bick". Utiliza celdas lógicas prediseñadas tales como compuestas AND, compuertas OR, multiplexores y flip-flop's, se les conoce como celdas estándar [4]. en la figura 2 puede un esquema de un CBIC y en la figura 3 un esquema real de un CBIC hecho con un programa de diseño para ASIC.

Figura 2: ejemplo esquema interno de un CBIC.

Figura 3: Vista de un CBIC hecho con un programa de diseño.

Las áreas de las CBIC conocidas como bloques flexibles están compuestos por columnas de celdas estándar como una pared de ladrillos. Las áreas de las celdas estándar pueden ser utilizadas en combinación con celdas mucho más grandes o quizás con microcontroladores o microprocesadores conocidos como megaceldas. Las megaceldas también son llamadas megafunciones, bloques completamente configurables, macros de nivel de sistemas (SLM's), bloques fijos, núcleos, o bloques de funcionalidad estándar (FSB's).

Los diseñadores de estos ASIC's solo definen el lugar de las celdas estándar y la interconectividad dentro de un CBIC. Sin embargo, la celda estándar puede ser ubicada en cualquier lugar de la pastilla de silicio; esto permite que todas las mascaras de un CBIC puedan ser configurables para un consumidor en particular. La ventaja de CIBIC es que los diseñadores ahorran tiempo y reducen el riesgo al utilizar librerías de celdas precaracterizadas y probadas, diseñadas utilizando las técnicas de una celda completamente configurable. Adicionalmente cada celda estándar puede ser optimizada individualmente. Durante el diseño de cada celda de la librería, cada transistor ha sido elegido para maximizar la velocidad y el área que ocupa en el IC. La desventaja es el tiempo o costo de diseño o la compra de la librería de celdas estándarizadas y el tiempo que requiere fabricar todas las capas del ASIC para el nuevo diseño.

El diseño de celdas estándar permite la automatización del proceso de ensamble de un ASIC. Grupos de estas celdas pueden acomodarse en forma de columnas, las columnas forman pilas verticales para formar a su vez bloques flexibles rectangulares. Puede interconectarse a otro bloque de celdas estándar de otro bloque o con otros bloques completamente configurables. Por ejemplo, puede desearse incluir una interfaz específica o un microcontrolador junto con algo de memoria. El bloque del microcontrolador puede ser una megacelda fija, a partir de los bloques puede generarse memoria utilizando un compilador de memoria y un controlador de memoria personalizado que puede construirse dentro de un bloque de celdas estándar.

ASIC's basdos en arreglos de compuertas (Gate Array).

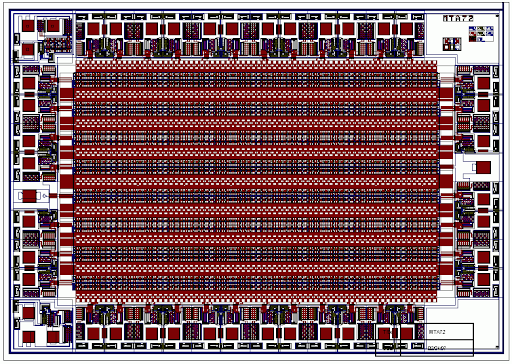

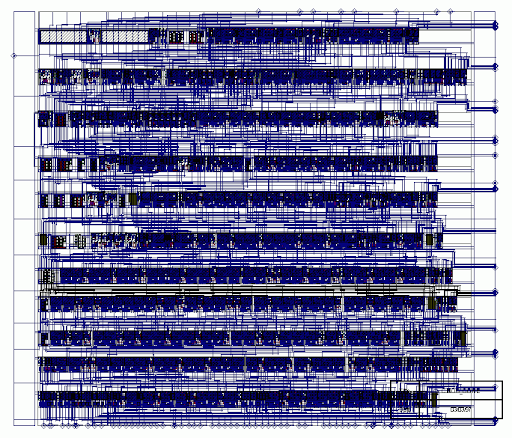

En un ASIC's basado en arreglo de compuertas los transistores están predefinidos en una oblea de silicio. Los patrones de definición de los transistores de un arreglo de compuertas y el elementos mas pequeño es replicado para hacer la base del arreglo, así como los dibujos de la porcelana en el piso, a este diseño primario se le llama la celda primitiva. Solo la capa superior tiene definida las interconexiones entre los transistores. Para distinguir este tipo de arreglo de compuertas de otros tipos de arreglos de compuertas este frecuentemente es llamado mascara de arreglo de compuertas o MGA por sus siglas en ingles [4]. El diseñador elige de una librería de arreglo de compuertas celdas precaracterizadas o prediseñadas. Las celdas lógicas de la librería de arreglo de compuertas frecuentemente son llamadas macros. La razón de esto es que, el diseño layout de la celda base es el mismo para todas y la interconexión entre ellas es lo que puede configurarse libremente, el diseño de un ASIC con arreglo de compuertas se hecho en un programa de diseño se muestra en la figura 4.

Figura 4: vista del diseño de un ASIC con arreglo de compuertas.

Puede hacerse la difusión entre varias obleas de silicio de varios consumidores según sea necesario. Utilizando las obleas de silicio prefabricadas se reducen los tiempos de metalización requeridos para hacer un MGA. Algunos de los diferentes tipos de ASIC's basados en arreglo de compuertas existentes son:

- Arreglo de compuertas acanalados.

- Arreglo de compuertas sin acanalado.

- Arreglo de compuertas estructurado.

Estos términos son dados a los ASIC's de acuerdo a su modalidad de construcción, por ejemplo, cuando los transistores están acomodados en un MGA dejando un espacio entre las columnas de transistores para cablear se refiere al primer termino, en caso de no existir dicho canal entonces se utilizan las columnas de transistores no utilizados para el enrutamiento conexiones lo cual corresponde al segundo tipo. En un modelo estructurado de diseño se pueden observar ambos modos de construcción juntos dentro de un bloque configurable.

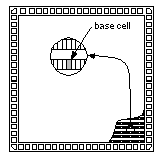

En la figura 5 puede observarse un arreglo de compuertas acanalado donde solo las interconexiones pueden ser configuradas, la interconexión utiliza espacios predefinidos entre las columnas de las celdas base y el tiempo de construcción puede tomarse entre dos días y dos semanas.

Figura 5: Esquema de un arreglo de compuertas acanalado.

En la figura 6 puede observarse la distribución de un arreglo de compuertas sin canales, aqui solo algunas de las mascaras de interconexión pueden configurarse. La densidad lógica es mucho más alta para este tipo de construcción.

Ffigura 6: Esquema de un arreglo de compuertas no acanalado.

En la figura 7 puede observarse un arreglo de compuertas estructurado, también es conocido como "masterimage", combina algunas de las características de los CBIC's y los MGA's. Una de las desventajas de los MGA's es el diseño fijo de la celda base del arreglo de compuertas, esto hace que la implementación de memoria sea de gran dificultad e ineficiente. En un arreglo estructurado de compuertas puede destinarse un área dedicada a una función específica lo cual resulta más cómodo para el diseño de celdas de memoria. En este tipo de arreglos solo las interconexiones son configurables y los bloques configurables pueden ser integrados al diseño.

Figura 7: Arreglo de compuertas estructurado.

En este último tipo de arreglos puede incrementarse el desempeño de un CBIC pero a un menor costo comparado con un MGA. Una desventaja de un arreglo de compuertas empotrado o embebido es que la función del elemento embebido es fija, por ejemplo, en un arreglo de compuertas empotrado que contiene 32 Kb de memoria, pero solo son necesarios 16 Kb de memoria entonces se desperdicia la mitad de la memoria. En la figura 8 puede observarse un diseño de un ASIC con arreglo de compuertas optimizado hecho en un programa de diseño.

Figura 8: Diseño de un ASIC con arreglo de compuertas optimizado.

Los ASIC's basados en arreglo de compuertas y los basados en celdas utilizan celdas predefinidas, pero la diferencia es que en una celda estándar puede cambiarse el tamaño de los transistores para optimizar el desempeño y la velocidad, pero el tamaño de los componentes en un arreglo de compuertas es fijo. Esto puede resultar en una disyuntiva entre el área de un arreglo de compuertas en el silicio.